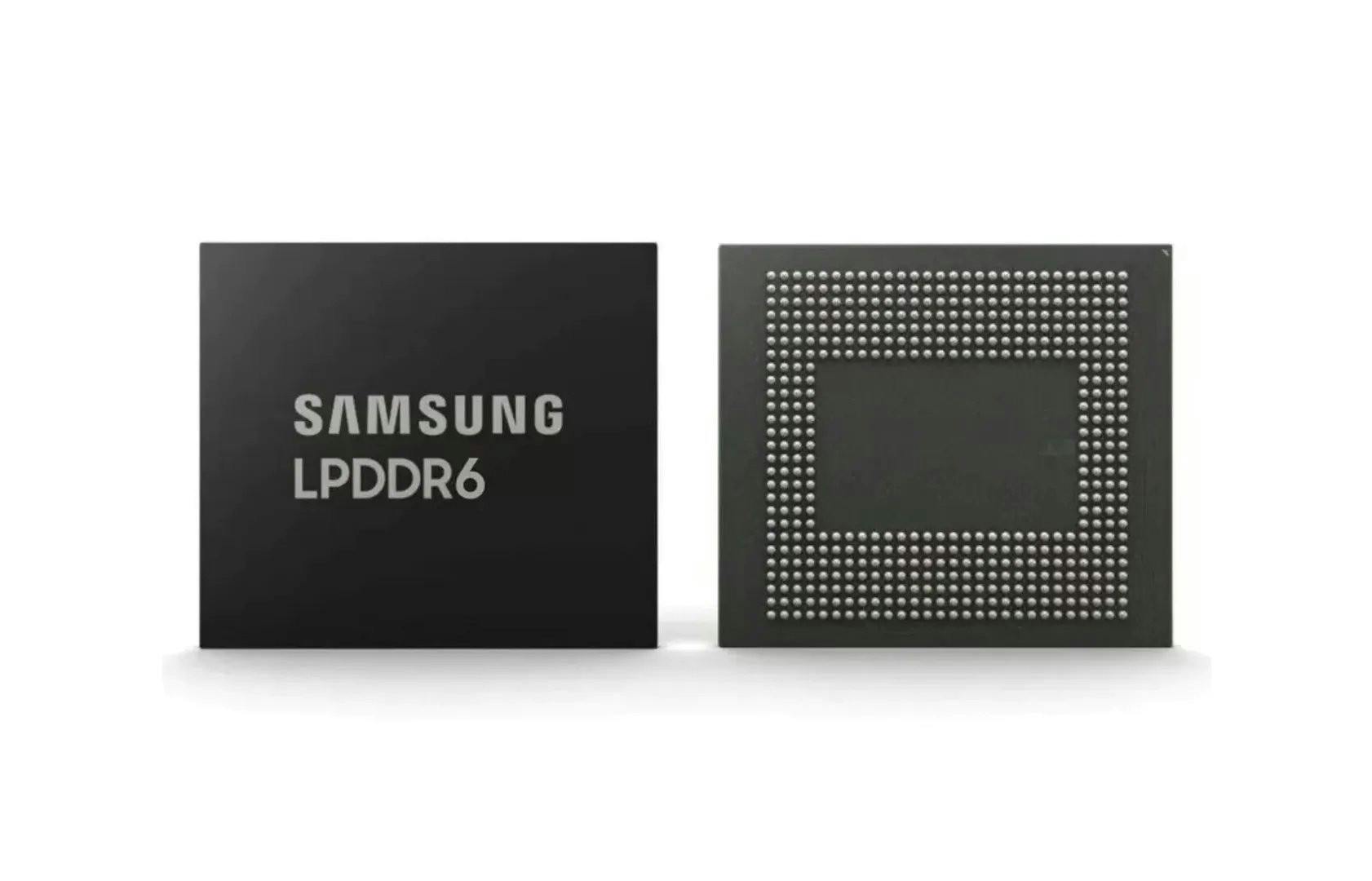

JEDEC 正式推出 LPDDR6 標準,滿足行動 AI 與高效能應用需求,記憶體效能再升級。

隨著行動與AI應用對於記憶體的效能需求不斷攀升,JEDEC固態技術協會正式公佈最新LPDDR6記憶體規格標準JESD209-6,加入更高頻寬、更低能耗,並且強化安全性等設計,預期將成為未來智慧型手機、AI PC、智慧汽車,以及能耗敏感型AI伺服器的重要記憶體設計規範。而聯發科、美光、Qualcomm、三星、SK hynix、新思科技 (Synopsys)等業者也同步表示,將針對LPDDR6規格展開對應開發與產品支援,藉此帶動相關生態系加速成熟。

相較於前一代LPDDR5記憶體規格,LPDDR6延續JEDEC對行動記憶體高頻寬、低延遲、小顆粒存取的發展方向,採用雙子通道架構設計,每顆晶片包含2組子通道、每組子通道具備12條資料訊號線 (DQ),搭配4條命令/位址 (CA)訊號線,在降低焊球數量 (Ball Count)的同時,進一步提升資料傳輸效能與速度,並且改善PCB設計複雜度。

針對大容量與多工運算需求,LPDDR6引入「靜態效率模式」 (Static Efficiency Mode),可最大化記憶體資源使用率,並且支援動態突發長度切換 (on-the-fly burst length),靈活對應32 Byte與64 Byte資料存取需求。此外,透過動態調整的寫入終端電阻 (NT-ODT),可根據不同運算負載,自動調整訊號完整性,提升高頻運作下的穩定性。

在功耗管理方面,LPDDR6採用更低電壓的VDD2電源設計,相較LPDDR5能更進一步降低能耗,並且強制配置兩個VDD2電源路徑,確保供電穩定性,同時也支援交替時脈命令、低功耗動態電壓頻率調節 (DVFSL),可在低頻運作時動態降低電壓,讓功耗表現最佳化。

而「動態效率模式」 (Dynamic Efficiency Mode)則針對低頻寬應用設計,可透過啟用單子通道讓功耗降低。另外,LPDDR6也支援局部自動刷新與主動刷新,藉此更有效降低刷新期間的耗電量。

因應AI與智慧裝置對資料安全與系統穩定性的要求,LPDDR6導入「每行啟動計數」 (PRAC)機制,強化DRAM內部資料完整性偵測,並且透過「Carve-out Meta模式」劃設特定記憶體區域,讓關鍵任務運作時更加安全。

安全性部分也支援可程式化連結保護、內建ECC錯誤修正,搭配CA奇偶校驗、錯誤清除與自我檢測 (MBIST),全面提升錯誤偵測與修復能力,讓高可靠性運算場景提供更充足保障。

隨著聯發科、三星、Qualcomm、美光、SK hynix、新思科技等廠商同步宣布展開LPDDR6相應開發,未來可望在高階智慧手機、AI PC、智慧車載系統、雲端與邊緣AI運算平台等市場快速落地,預期最快2026年將有首批搭載LPDDR6的產品問世,進一步推動智慧運算時代的性能與效率邁向全新高度。