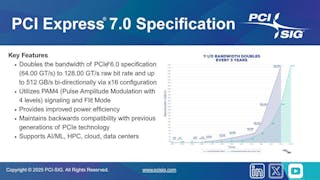

雖然PCI-SIG的PCIe 6.0的合規計畫還未啟動,不過隨著運算產業對高速通用介面的需求不斷升溫,且在異構加速的HPC與AI進一步產生系統高速互聯的需要,PCI-SIG與成員已經著手制定PCIe 7.0的初步規格;其中知名電子設計自動化軟體與工程服務公司Cadence益華在2024年的PCI-SIG DevCon開發者大會展示利用光通訊傳導的PCIe 7.0技術。

在新一代的AI與HPC不僅追求更高的頻寬與更低的延遲,同時也在環境永續議題下需要著重能源效率,一方面電訊號雖然至今仍是PCIe(甚至包括NVIDIA的NVLink也是電訊號)的主要訊號乘載方式,但具備更高速度傳輸可能性、更低延遲且更不耗能的光通訊勢必成為下一階段超高速通用介面的重點技術。

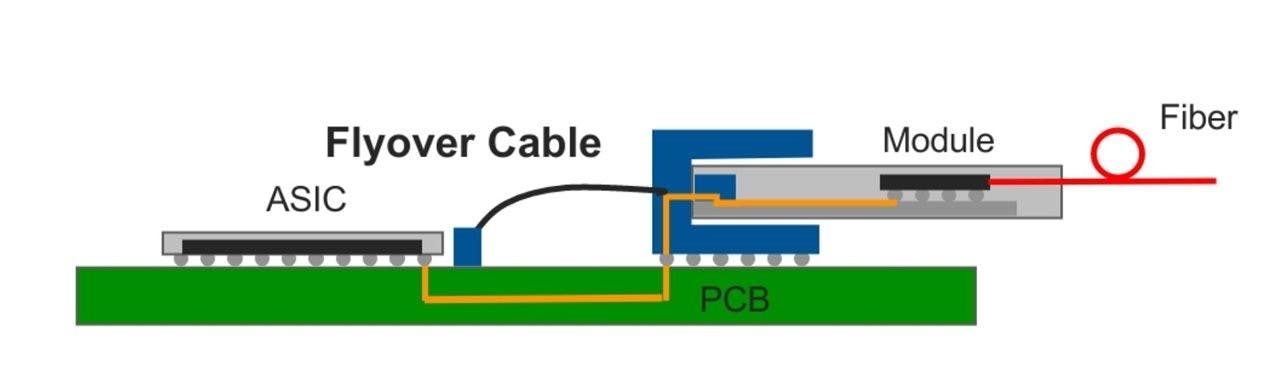

雖然光纖網路具有上述的優點,不過由於現行分散式運算會將系統分布在多個位於不同建築物的節點,光通訊將會遇到功率牆的問題,但也不能一味增加功率導致系統耗電上升,故現在的解決方法是透過使用邏輯晶片的non-retimed的線性拓樸,相較典型使用DSP進行的retimer光訊號解決方案,線性可插拔光學(LPO)鏈路可有像降低能耗與延遲,且相對使用DSP成本更低;Cadence在此次的PCI-SIG展示透過non-retimed線路的PCIe 7.0子系統測試板超過128GT/s的傳輸性能。