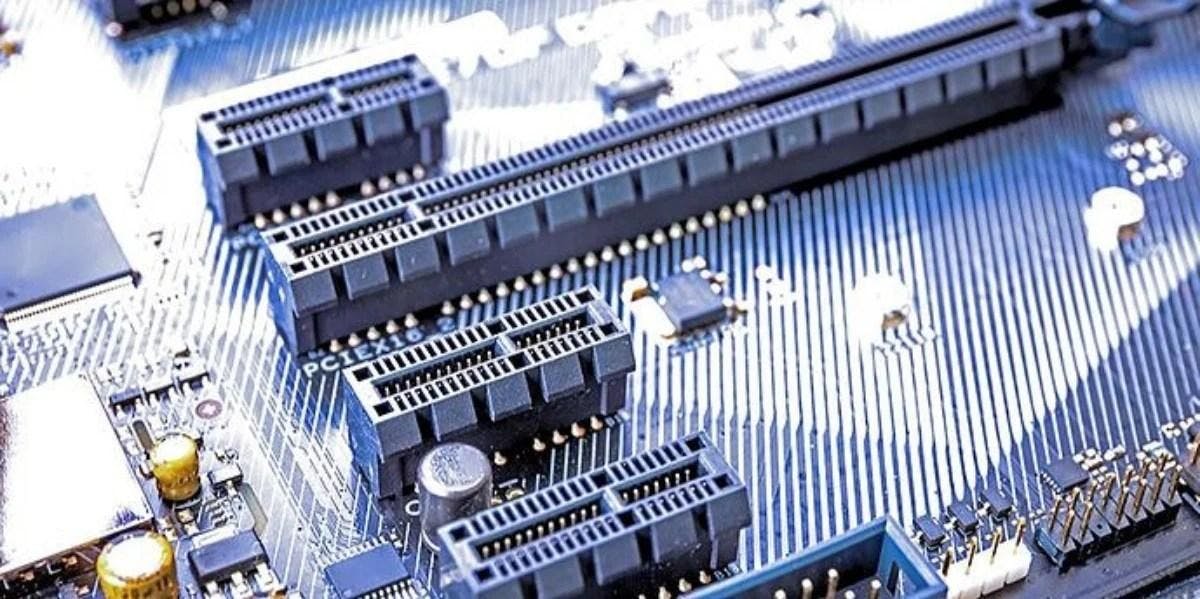

PCI-SIG 公布 PCIe 7.0 規格 將光纖應用納入 PCIe 設計範疇

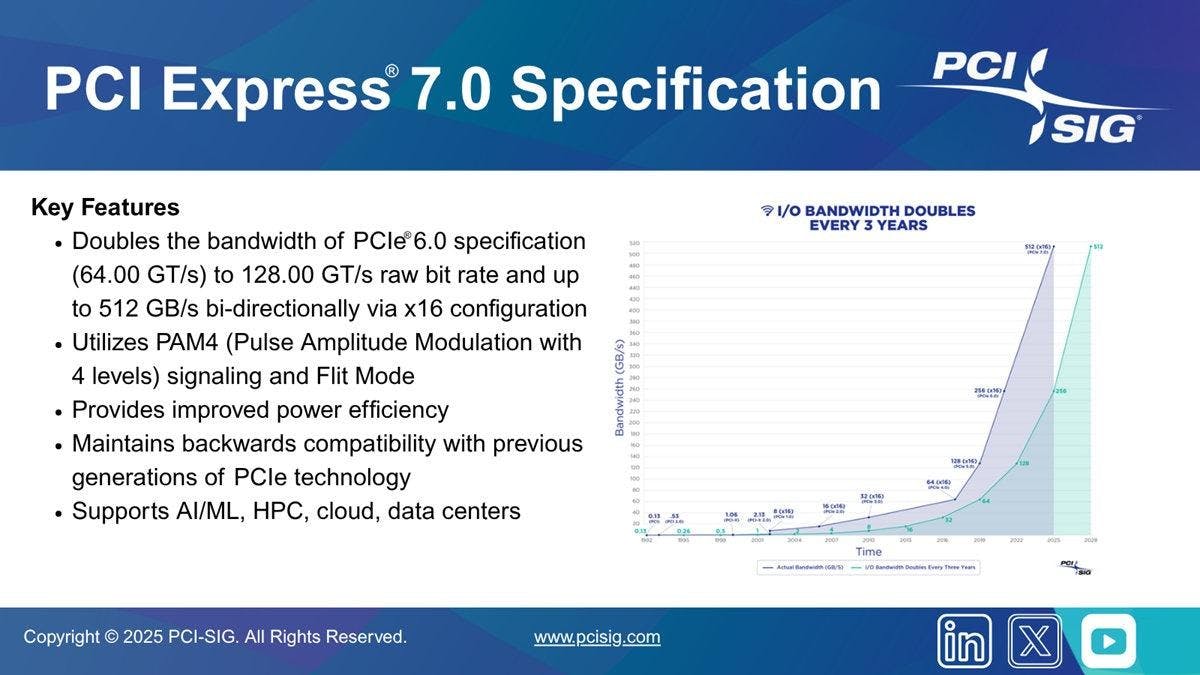

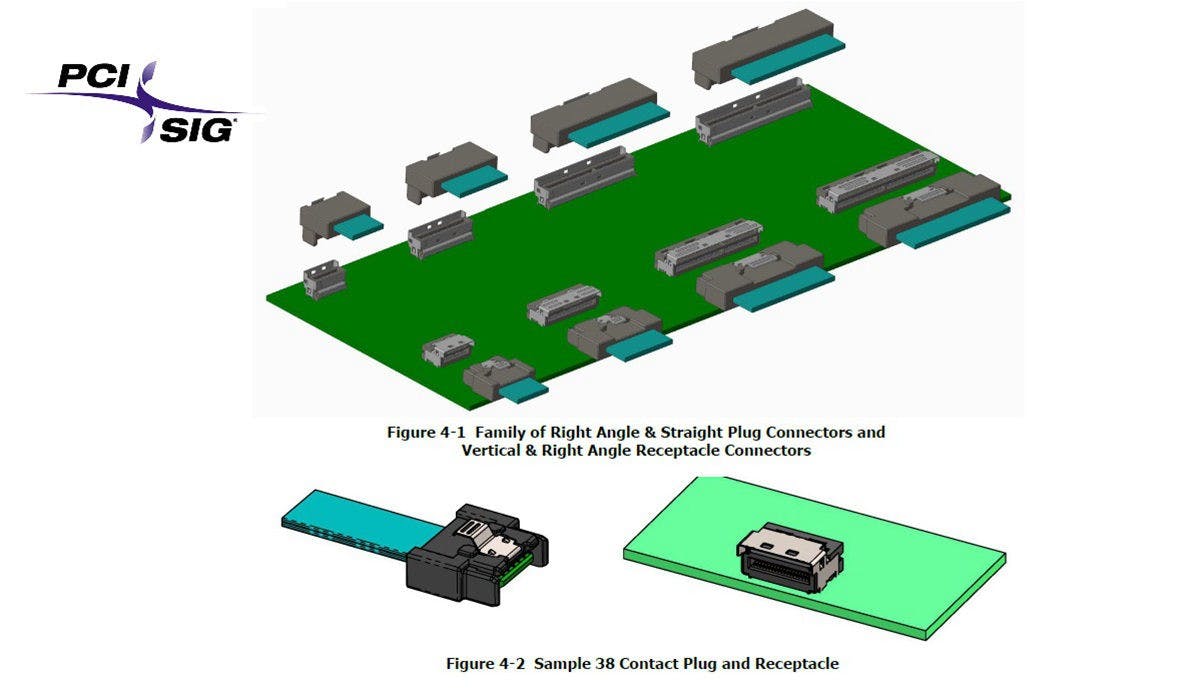

PCI-SIG 正式發表 PCIe 7.0 標準,新增光纖應用設計範疇,並宣布開始研發 PCIe 8.0。 先前釋出多個修訂版本之後,PCI-SIG終於宣布推出PCIe 7.0正式規範,標榜能以128.0 GT/s傳輸規格滿足當前人工智慧運算的頻寬需求。此外,PCI-SIG更宣布在PCIe 6.4及PCIe 7.0設計規範納入光纖應用,藉此對應更高數據傳輸表現,同時也讓光纖應用成為設計標準。 PCIe 8.0規範著手規劃,但尚未具體規格細節 同時,PCI-SIG更預告已經著手探索PCIe 8.0規範,但目前仍處於相當早期規劃階段,尚未公布具體規格細節。 PCIe 7.0設計可對應最高高達512

1 個月前