PCI-SIG 正式發表 PCIe 7.0 標準,新增光纖應用設計範疇,並宣布開始研發 PCIe 8.0。

先前釋出多個修訂版本之後,PCI-SIG終於宣布推出PCIe 7.0正式規範,標榜能以128.0 GT/s傳輸規格滿足當前人工智慧運算的頻寬需求。此外,PCI-SIG更宣布在PCIe 6.4及PCIe 7.0設計規範納入光纖應用,藉此對應更高數據傳輸表現,同時也讓光纖應用成為設計標準。

PCIe 8.0規範著手規劃,但尚未具體規格細節

同時,PCI-SIG更預告已經著手探索PCIe 8.0規範,但目前仍處於相當早期規劃階段,尚未公布具體規格細節。

PCIe 7.0設計可對應最高高達512 GB/s的雙向傳輸速率表現

在此次成為正式規範的PCIe 7.0設計中,標榜其數據傳輸速率可達128.0 GT/s,更可在x16配置下實現高達512 GB/s的雙向傳輸速率,主要因應人工智慧/機器學習、800G乙太網路、雲端運算及日後預期普及的量子運算作準備。

此外,PCIe 7.0設計也採用PAM4 (四級脈衝幅度調變)訊號和基於Flit (流量控制單元)的編碼設計,藉此進一步提高能源使用效率,並且確保與前面幾代的PCIe設計規格相容。

PCI-SIG總裁暨主席Al Yanes表示,隨著人工智慧應用持續快速擴展,下一代PCIe技術將滿足佈署人工智慧的數據密集型市場頻寬需求,包括超大規模數據中心、高性能計算 (HPC)、汽車,以及軍事/航空航天等應用場景。同時,市場分析業者More Than Moore的首席分析師暨執行長Ian Cutress也指出,目前多數資料中心已經做好佈署基於PCIe 7.0技術的網路架構相關準備。

光纖應用成為PCIe 6.4與PCIe 7.0設計規範標準之一

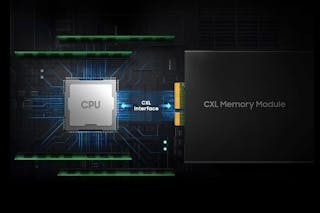

而PCI-SIG也宣布新版光互連規範修訂,並且加入PCIe 6.4與PCIe 7.0設計規範,其中新增基於PCIe重定時器 (retimer)的設計,藉此讓光纖應用能成為PCIe技術標準化規格。

在此標準之下,將使PCIe 6.4與PCIe 7.0設計規範無縫支援各種光連接技術,實現現有符合PCIe 6.4及PCIe 7.0規範設計交換器、根複合體 (root complex)裝置與端點晶片設計之間的光互連需求,同時也能藉由光連接技術擴充跨機架及pod組合的連接範圍,同時也加入跨電域及光域進行多路複用、資料映射使用需求,同時也能實現比銅纜線設計更為緊湊的晶片設計方案。