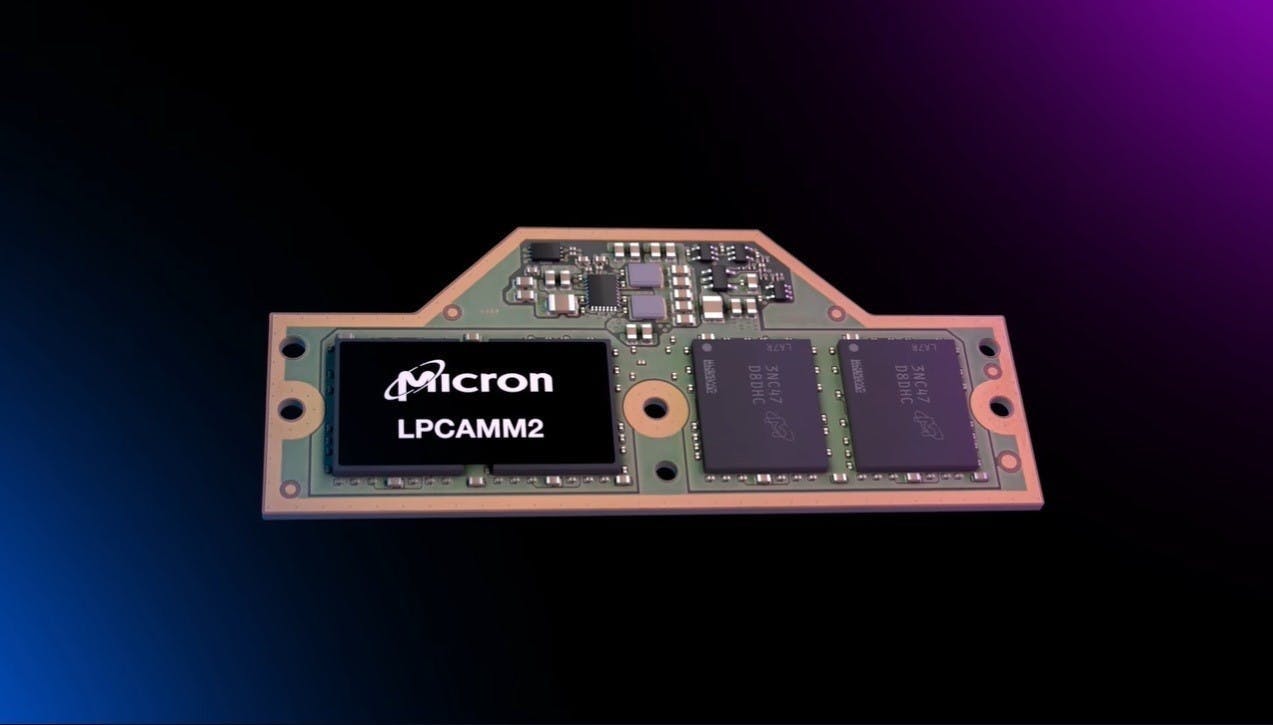

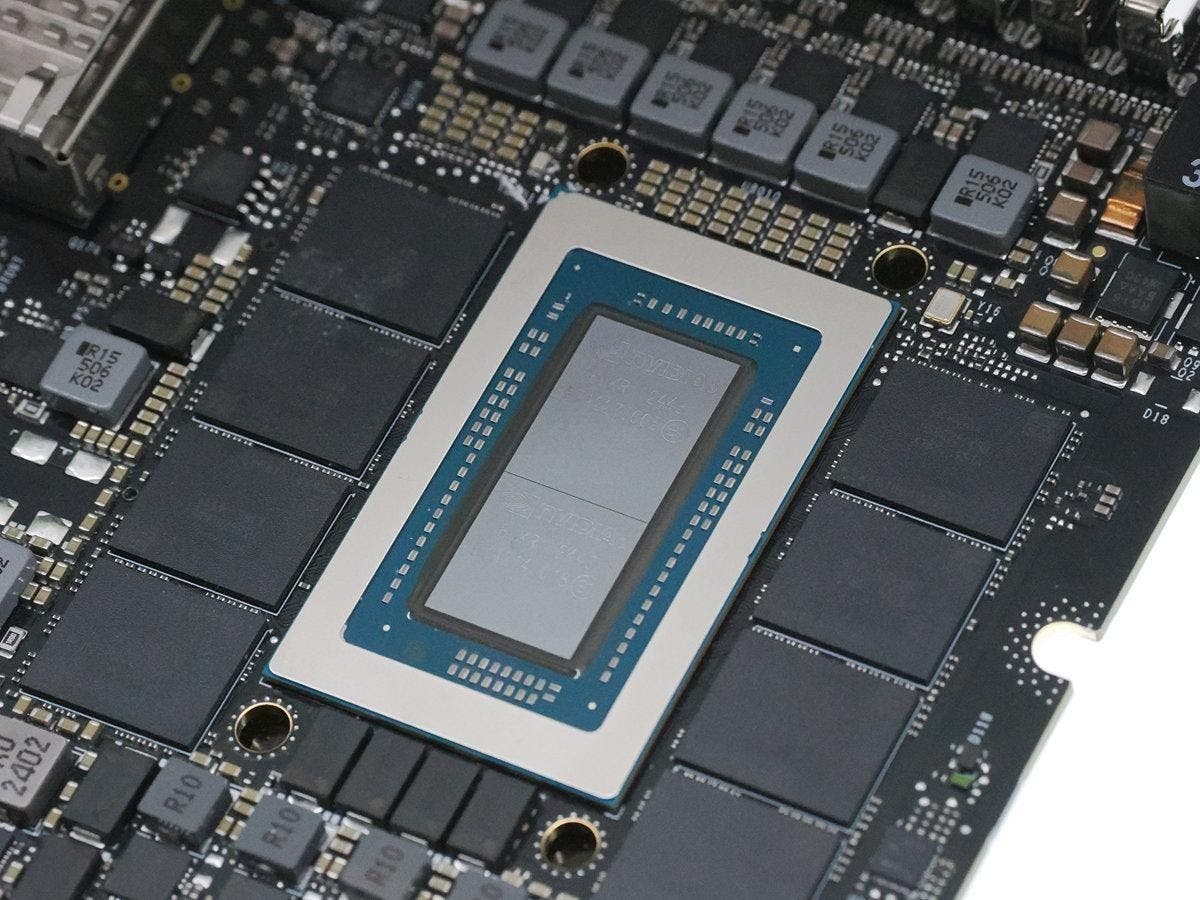

JEDEC在2025年7月9日宣布LPDDR6標準JESD209-6,寄望LPDDR6能提升行動裝置與AI應用的性能,並適用於智慧手機、電腦、智慧汽車與著重能耗的AI伺服器等。包括聯發科、美光、高通、三星、SK Hynix、新思科技等都宣布積極因應LPDDR6提供開發與支援。

LPDDR6採用雙子通道架構,並保持32bit的小存取粒度,每個晶片有兩個子通道,每個子通道有12條資料訊號線(DQ),每個子通道包括4個命令/位址(CA)訊號,並透過最佳化減少Ball Count提升資料存取速度,靜態效率模式可提供大容量記憶體配置並最大限度提高記憶體資源利用率,此外具備靈活的數據存取,動態突發長度控制,支援32B與64B存取,動態寫入NT-ODT可使記憶體依據工作負載需求調整ODT,進而提升訊號完整性。

另外LPDDR6採用比LPDDR5更低電壓、低功耗的VDD2電源,同時強制使用兩個VDD2電源,另外還包括可提升效能與效率的交替時脈命令,低功耗動態電壓頻率調節(DVFSL)可在低時脈運作降低Vdd2電源進而減少能耗,動態效率模式可利用單一子通道實現低公耗、低頻寬應用,此外支援部分自主更新與主動更新,減少更新產稱的能耗。

在安全性部分,LPDDR6在每行啟動計數(PRAC)支援DRAM資料完整性,以及透過關鍵任務分配特定記憶體區域提升整體系統可靠性的Carve-out Meta模式,支援可程式連結保護方案與ECC,可支援CA奇偶校驗、錯誤清除與記憶體內自我檢測(MBIST),藉此提升錯誤檢測與系統可靠性。