CXL 技術由 Intel 與多家企業推動,加快人工智慧運算效率,實現記憶體與加速器間更快互連。

CXL (Compute Express Link)技術規格是由Intel在2019年3月主導,由諸多業者加入合組聯盟,期望透過此高速介面標準解決CPU與加速器如GPU或FPGA之間溝通延遲,以及傳輸頻寬不足等問題,藉此因應日趨複雜的運算工作需求,尤其是當前日漸增長的人工智慧應用發展。

什麼是CXL?

傳統運算架構中,CPU與GPU之間溝通是透過PCIe通道與PCIe設計協議,雖然PCI-SIG逐年推進PCIe規格設計,但顯然仍趕不上當前更龐大的數據運算需求,因此CXL技術規格的誕生,實際上就是為了改善CPU、GPU等運算元件之間溝通延遲、傳輸頻寬不足問題。

即便市場已經有NVIDIA提出其NVLink技術,但其僅適用於NVIDIA的GPU之間溝通,而CXL技術則可對應更多運算元件,同時也能夠成更大市場生態,藉此推動更多複雜運算應用發展。

CXL技術規格建立在既有PCIe 5.0、6.0規範,已經提出CXL 1.0、1.1、2.0,以及目前的3.0版本,其中1.0、1.1版本允許CPU直接與其他運算元件直連,但單次僅能實現一對一連結,直到2.0版本才能做到多對多連結,藉此增加更多運算配置彈性,同時更可動態分配記憶體使用區塊,藉此增加運算使用彈性,另外也增加資料加密機制,藉此提供更安全的運算表現。

而目前進展的CXL 3.0版本,則是提供多層式交換連接,更加入網狀 (Mesh)或環狀 (Ring)等非樹狀的交換連接架構,讓CPU能更具彈性地與更多運算元件進行溝通連結,並且改善多重存取能力,藉此實現更複雜、規模更龐大的運算元件連接溝通。

相比1.0、1.1與2.0版本是以PCIe 5.0通道建立連結,最高可在單向傳輸實現最高每秒63GB的資料傳輸頻寬,或是在雙向時實現最高每秒126GB的資料傳輸頻寬,目前推進的3.0版本則改為PCIe 6.0通道規格,資料傳輸頻寬約比先前的版本提升一倍。

CXL技術以開放標準架構推動運算資料高速傳輸

CXL技術本身採開放標準架構設計,並且由Intel、三星、VMware在內業者共同推動其生態成長,並且能用於各類處理器、加速器、記憶體緩衝區塊,甚至各類I/O連接設計,藉此實現高速傳輸與低延遲數據通訊,讓當前記憶體容量、傳輸頻寬能突破既有規格瓶頸,並且帶動更大運算效能。

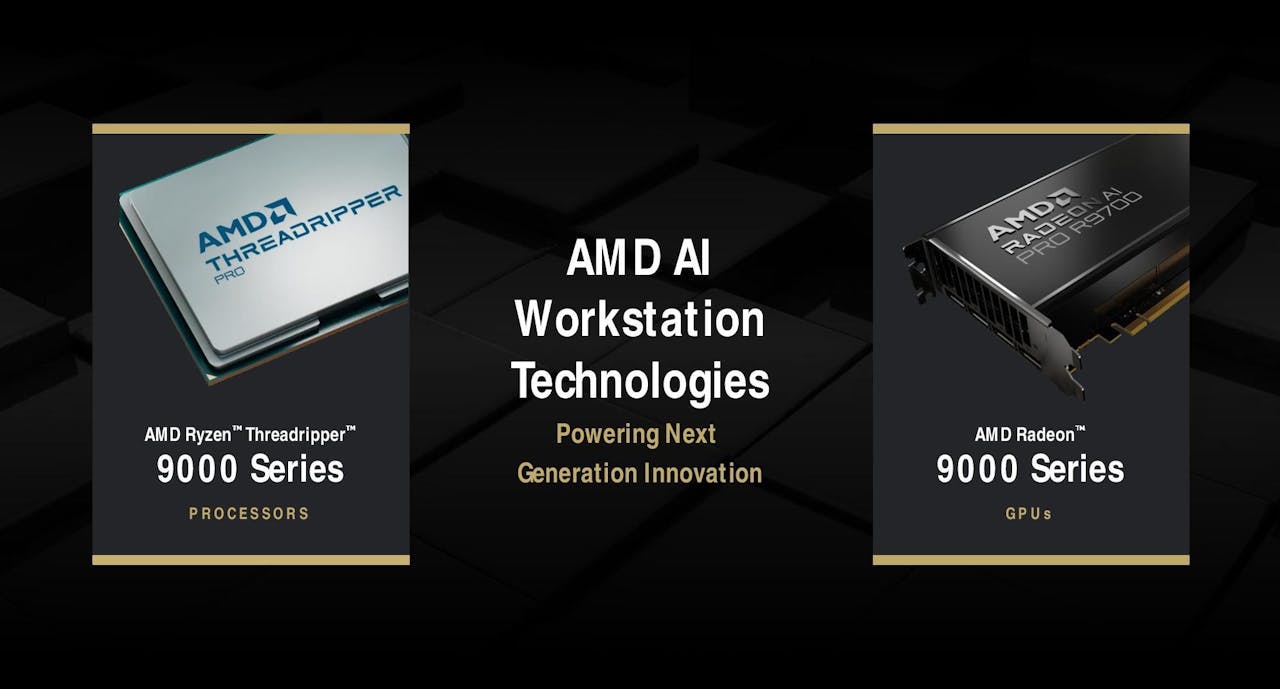

例如,Intel作為為CXL技術主要推動者之一,目前已經在其代號Sapphire Rapids的第四代Xeon Scalable系列處理器採用CXL設計,而AMD也在其代號「Genoa」的第四代EPYC處理器導入CXL技術,三星等記憶體大廠也積極開發支援CXL技術的DRAM記憶體模組,除此之外,記憶體模組、CXL控制器IP、伺服器ODM/OEM等業者也有所進展,顯示2025年相關軟硬體生態系成形,邁入實用化。

三星藉由CXL技術結合其DRAM記憶體設計打造的CMM-D (CXL Memory Module–DRAM)模組,可依照運算需求動態擴充記憶體容量配置,藉此符合數據密集型工作負載需求,同時也能因應日後算力需求增加擴充記憶體容量。而三星打造符合CXL 2.0規格的128GB DRAM記憶體,在使用PCIe 5.0介面設計情況下,能顯著提升記憶體容量與頻寬,並且滿足人工智慧及高效能運算應用場景。

為加速下一代記憶體解決方案的商業化,三星積極擴展CXL技術生態,與Intel、瀾起科技 (Montage Technology)、Supermicro、雲達科技 (QCT)、微星科技 (MSI)、技嘉科技 (GIGABYTE)、H3 Platform等企業展開合作。

例如,在2024年Red Hat Summit活動,三星與Red Hat推動開源技術及標準化合作,並且在真實用戶使用場景驗證CXL記憶體技術可行性。

產業及市場展望

CXL技術主要目標是解決CPU、GPU,乃至於FPGA、加速器等運算元件與記憶體之間的低延遲、高頻寬連接需求問題,並且率先用於資料中心、人工智慧訓練,以及高效能運算 (HPC)等需求,例如AWS、Azure、Google Cloud等雲端服務業者藉由CXL架構打造動態記憶體池,藉此提高雲端運算環境資源分配使用效率,另外也能因應當前人工智慧訓練、推論應用需求彈性佈署記憶體容量與整體資料傳輸頻寬。

在當前人工智慧、高效能運算等需求持續增加情況下,對於記憶體資源應用的需求也會相對增加,將推動CXL技術進入更多應用。

在半導體領域也能看見Intel、AMD等處理器業者加入使用CXL技術,使其處理器產品能對應CXL架構下的運算模式,並且能藉由容量更大、傳輸頻寬更高形式提升資料運算效率。另外也能看見包含Astera Labs、Montage、Rambus等業者加快推出新版交換器與記憶體擴展解決方案,進而帶動更龐大的運算規模成長。

因此,接下來預期將看見CXL技術提高記憶體佈署的彈性,縮減CPU、GPU等運算元件之間延遲與資料傳輸頻寬問題,進而加速人工智慧等先進技術成長。而CXL技術也將擴展至模組化設計的邊緣伺服器,藉由分散架構形式讓運算資源能彈性擴展。

同時,CXL聯盟也將整合包含制訂PCIe規範的PCI-SIG,或是開放運算計畫 (Open Compute Project,OCP)等標準組織資源,藉此加快CXL技術版本更新,使其配合推動軟硬體協同最佳化。

然而,目前CXL技術應用成本與佈署複雜度相對較高,部分技術也尚未成熟,加上作業系統、驅動程式與應用程式也需要針對CXL記憶體架構作調整、最佳化,因此在應用發展仍會面臨一些阻力。

不過,在早期針對提高加速器取用記憶體資源需求提出的CCIX (Cache Coherent Interface for Accelerators)技術,其不少成員已經陸續轉向加入CXL技術規範,加上由Intel、AMD、Qualcomm、Google等業者推動的UCIe規範也相容CXL技術,因此對於CXL技術後期發展更為有利,同時也可能在未來3-5年成為資料中心與高效能運算不可或缺技術。