2017年2月中旬,Intel宣佈開始發貨代號「Kittson」的Itanium 9700系列處理器,是繼2012年的Itanium 9500系列「Poulson」後,睽違五年的「更新」,除了聊勝於無的稍稍提高點時脈,仍沿用與前代相同的老舊32nm製程,與充滿懷舊風的DDR3-1067記憶體規格。Kittson將是Itanium的終點,一場糾纏著處理器巨人的二十年惡夢,也從此劃下了休止符。在今天,腦海中仍對Itanium存有印象者,恐怕不外乎骨灰級電腦玩家,或著年紀不小的企業IT人員吧。

不知道Itanium該怎麼念?科科們就請記得發音很像「唉坦你啞」就好了。

算上後繼的蝴蝶效應(NetBurst的悲劇),這場也許堪稱Intel史上最大災難的拖棚歹戲,其導火線源自於想進軍伺服器市場的Intel,和HP合作重新打造的全新指令集架構「IA-64」。在1987年,HP評估在1992年,其自家的PA-RISC處理器,難以實現每個時脈週期處理四個指令,所以進行超長指令集(VLIW)化PA-RISC的相關研究。

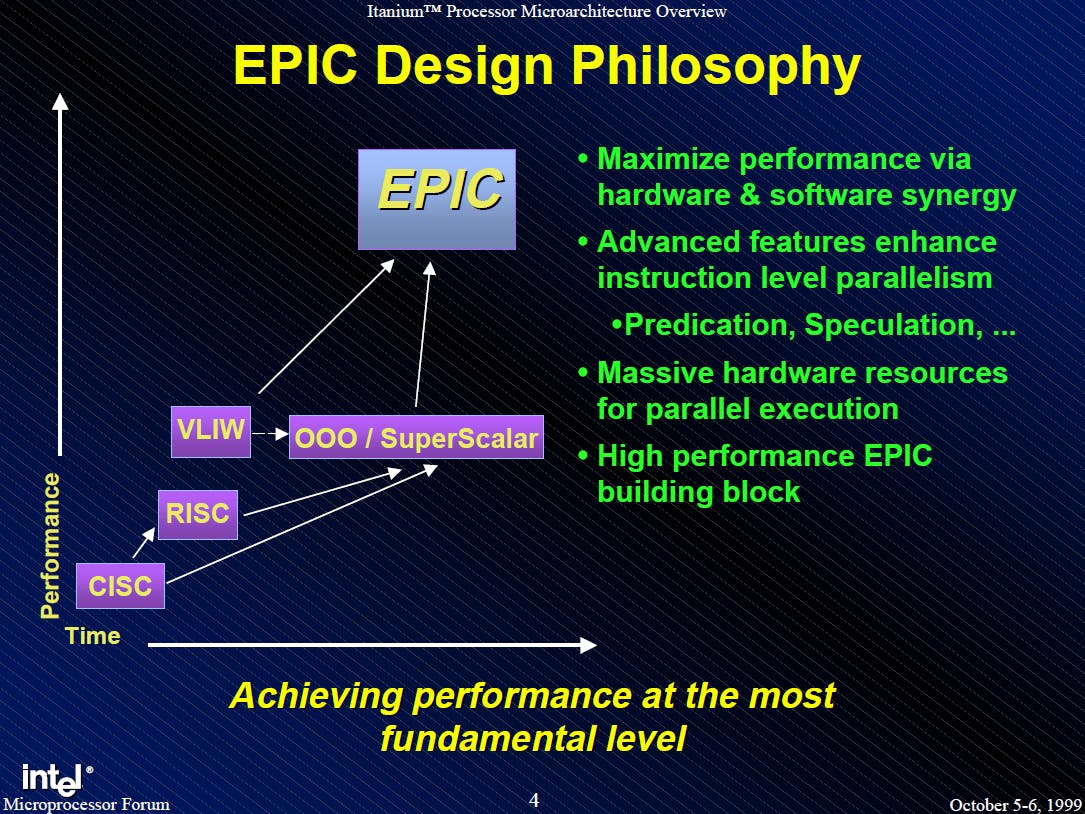

指令平行處理的2種作法

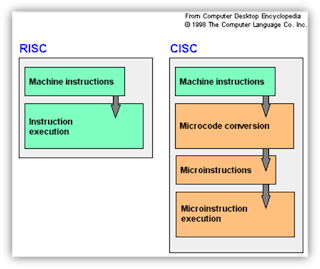

談到指令平行處理,一般而言,有兩種作法,一個是硬體手段的「超純量(Superscalar)」,今日我們看到多數高效能泛用處理器,幾乎都是動態指令排程兼具預測執行的超純量架構(當然早期也有循序靜態排程的超純量,如x86世界首發的Pentium),先前處理器資安漏洞連環爆,都是根源於此。

另一種則是軟體手段的「超長指令集(VLIW)」,指令集架構將多個運算打包在一起,透過編譯器「靜態」的一個蘿蔔一個坑的塞進去,優點是硬體設計比較簡單,等於把追求平行化的工作全部丟給軟體搞定,缺點是編譯器最佳化難度頗高,以及不易日後更動處理器微架構。

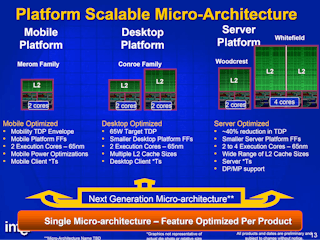

VLIW的IA-64就是Intel對先天不足、後天失調的x86指令集,最激烈的反動,身為電腦根本語言的指令集架構,徹底為了「便於編譯器開發者發掘出最極致的指令平行化」與「最簡單、最長壽的高效能處理器微架構」而量身訂做,Itanium則是這世上唯一相容IA-64指令集的處理器家族。

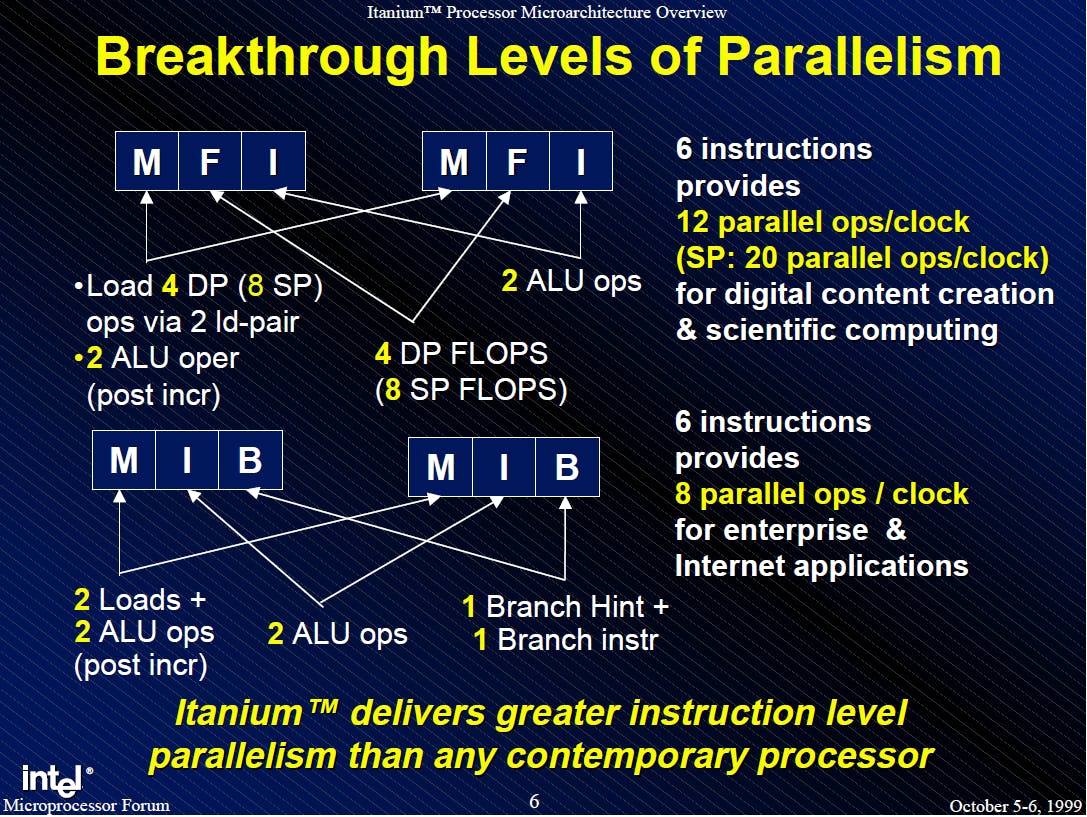

x86指令集最令人詬病的缺陷,莫過於指令編碼格式混亂,長短不一,不僅增加實作控制單元的複雜度(特別是發生例外和中斷時,如何迅速儲存和回復處理器狀態),因為不好做複數指令解碼器,也不利於研製高平行化的處理器微架構。IA-64指令包編碼統一128位元,包含3個41位元的運算指令,和標示最多32種指令排序的5位元,一勞永逸的根除宿疾,處理器只要同時執行2個指令包,就等於一次進行6個指令。x86亂無章法的運算元定址模式,也在IA-64上消失的無影無蹤。

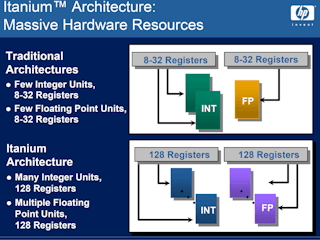

x86指令集缺乏足夠的資料暫存器(整數浮點各8個),頻繁發生的暫存器相依,嚴重限制了編譯器最佳化的彈性與指令平行化的潛力,Intel就在IA-64「要五毛,給十塊」,很豪邁的定義128個通用暫存器和128個浮點暫存器,遠超過當時主流RISC指令集的32個(講的嚴格一點是31個)。

IA-64設計精神Relax Limitation For Performance

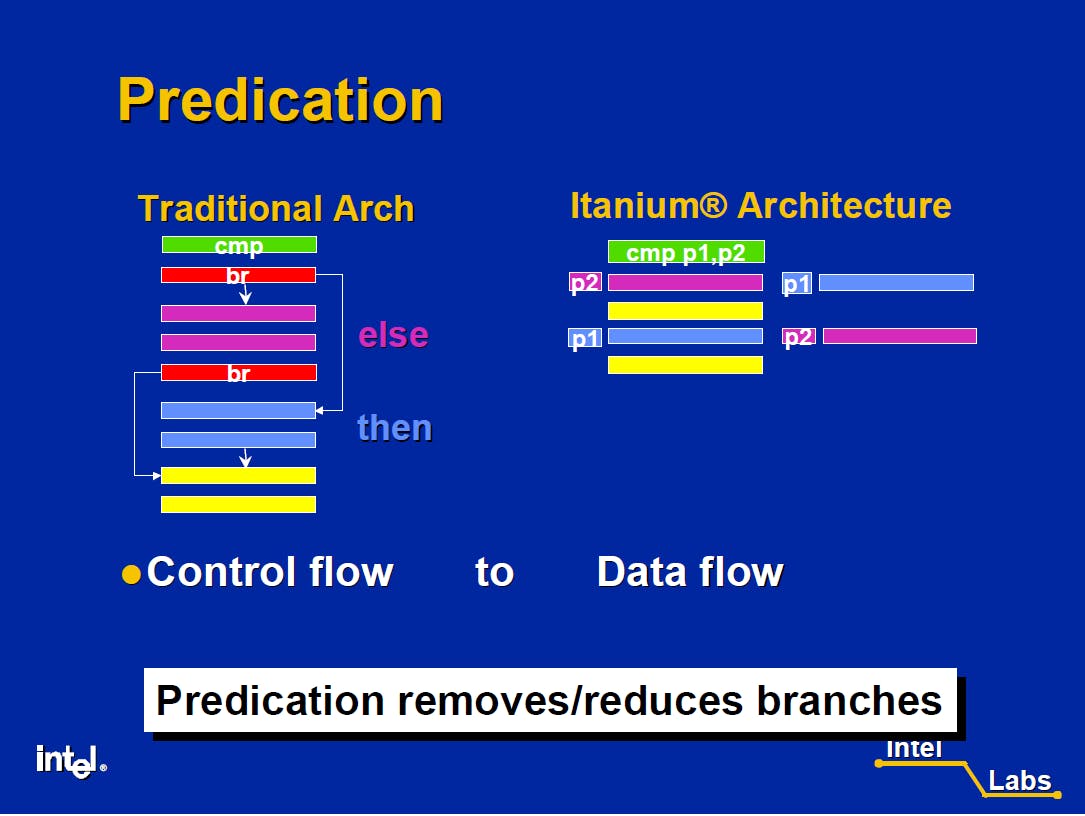

對付分支指令更是超級重頭戲,像利於降低分支負擔的引述執行(Predication),亦配備了專用的條件碼暫存器群,可應對更加複雜的軟體管線,而存放分支位址更有「專款專用」的暫存器配置。至於方便編譯器提前載入後面資料的預測載入機制(Speculative Load),加速程序呼叫的暫存器堆疊機制(Register Stack),攤平迴圈的暫存器輪轉機制(Register Rotation)等,無一不是極度豪華的「超重武裝」。

以前曾有人以 “Relax Limitation For Performance” 描述IA-64的設計精神,毫無過譽。事實上,IA-64的確比x86,甚至是其他的RISC,更適合用來打造簡單、省電、又高效能的處理器核心,核心晶粒面積和電晶體數量,也不到同時期Intel AMD x86處理器的一半,功耗表現更是異常的出色,這就是毫無包袱的嶄新指令集架構,與傲視世界的處理器研發能量,合而為一的成果。

還看不過癮嗎?讓我們繼續看下去「硬科技:回顧消失在歷史洪流的Intel旗艦處理器Itanium(中)」