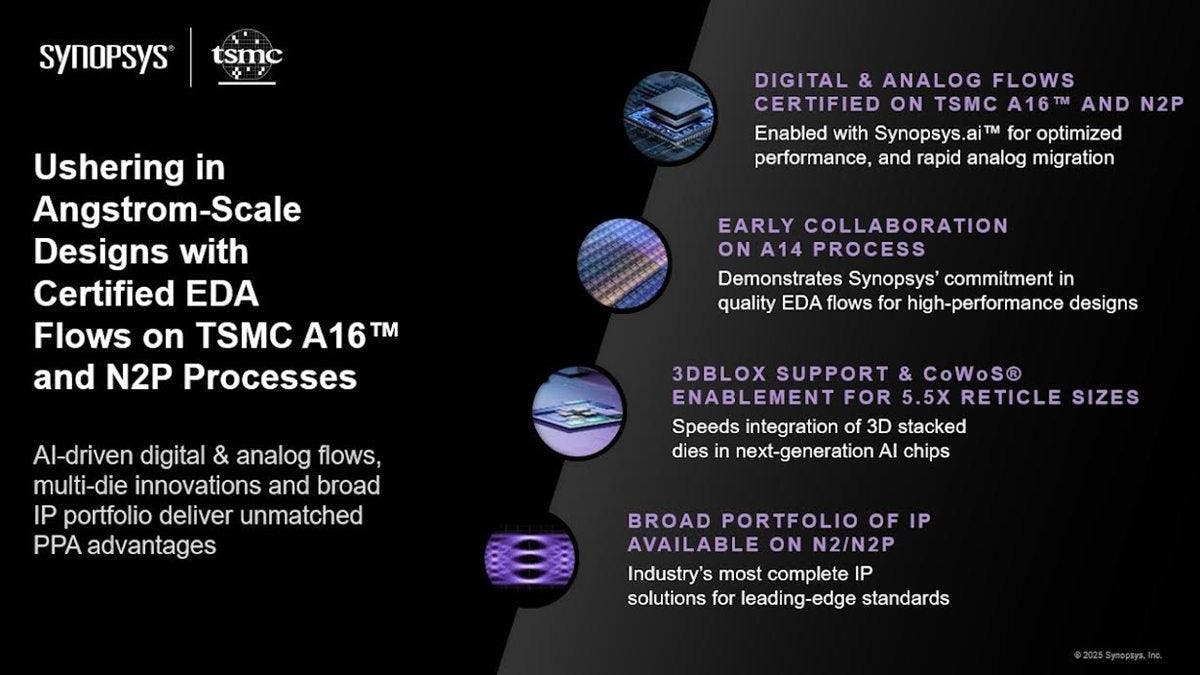

新思科技與台積電共同推動埃米級設計,於A16及N2P先進製程導入經認證的EDA流程

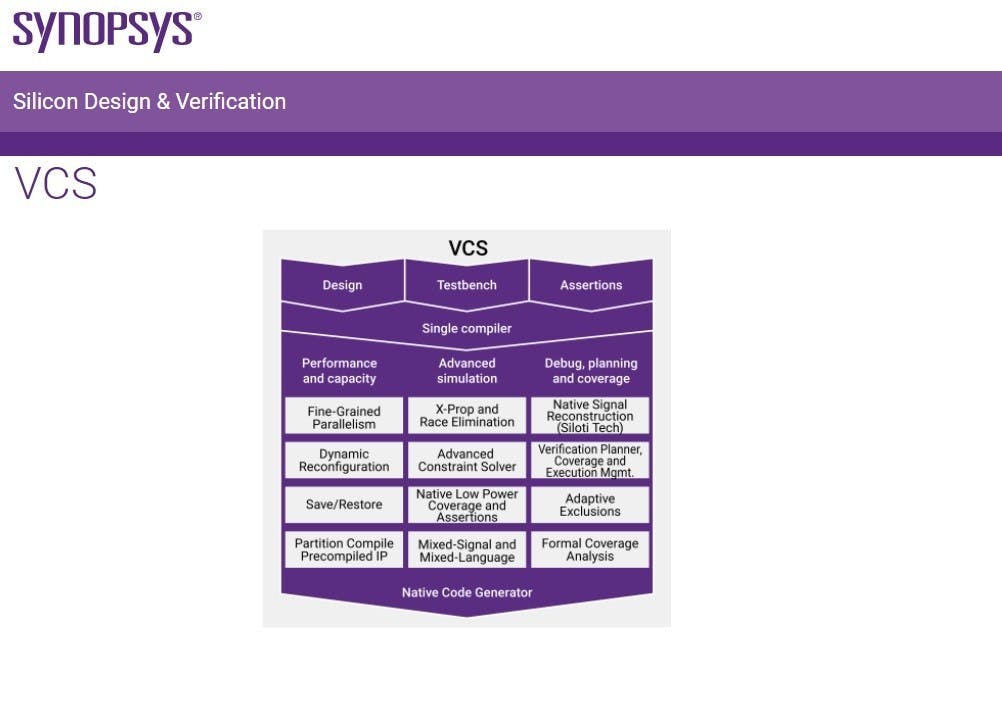

電子設計自動化(EDA)大廠新思科技Synopsys宣布與台積電共同合作推動埃米級(Angstrom-Scale)設計,以Synopsys.ai於台積電A16及N2P製程的數位與類比設計流程提供最佳化的效能與快速的類比設計遷移,同時新思科技的EDA開發作業亦與台積電在後續的A14製程進行早期合作。此外新思科技也針對次世代AI晶片的5.5倍光罩尺寸封裝、3D堆疊經歷的高速整合等,展開相關的3Dblox與台積電CoWoS技術協作,並針對如HBM4、1.6T乙太網路、UCIe、PCIe 7.0、UALink等業界通用高頻寬介面提供完整IP解決方案,使各種異質系統單晶片能提供新世代的高頻寬介面。 ▲台

1 個月前