Intel晶圓代工宣布未來節點互聯微縮技術突破,新材料、先進封裝提升電晶體容量與晶片對晶片速度

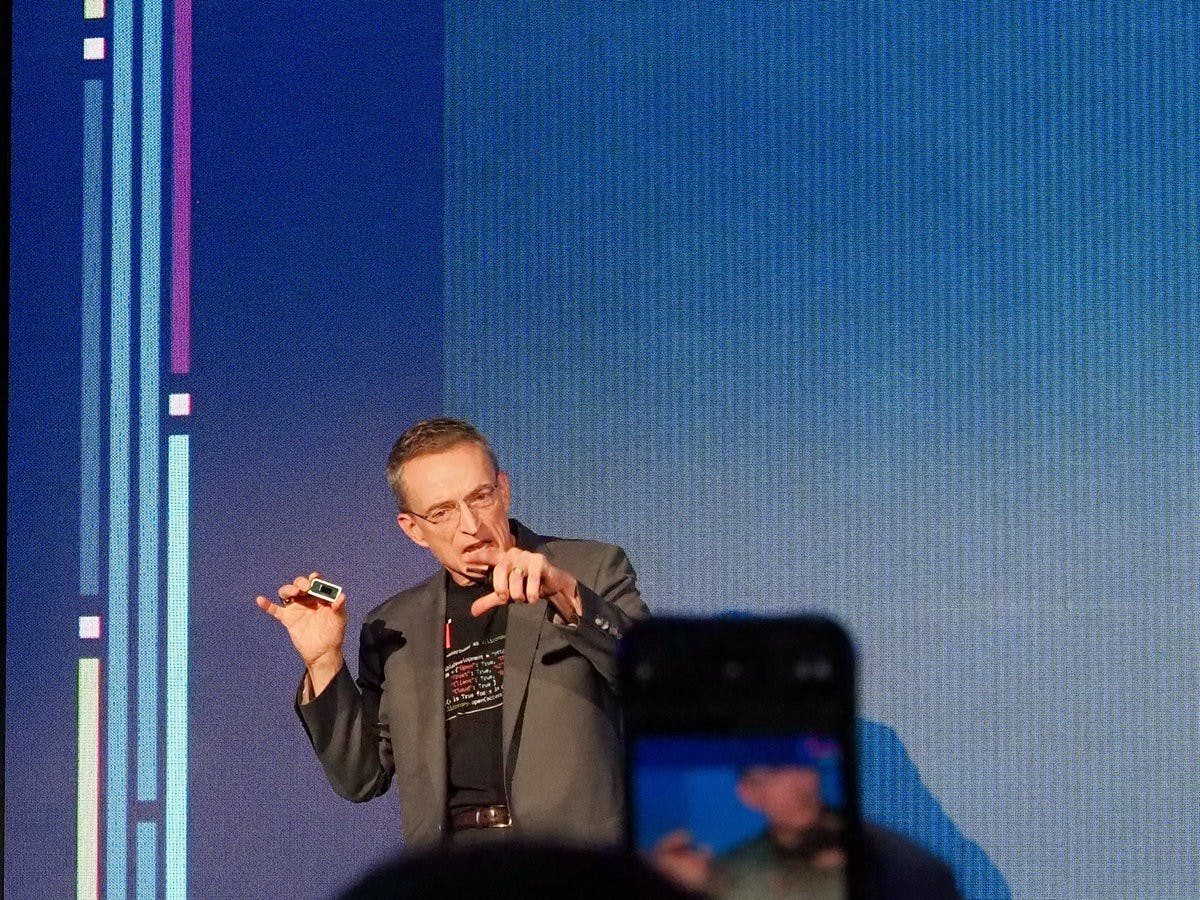

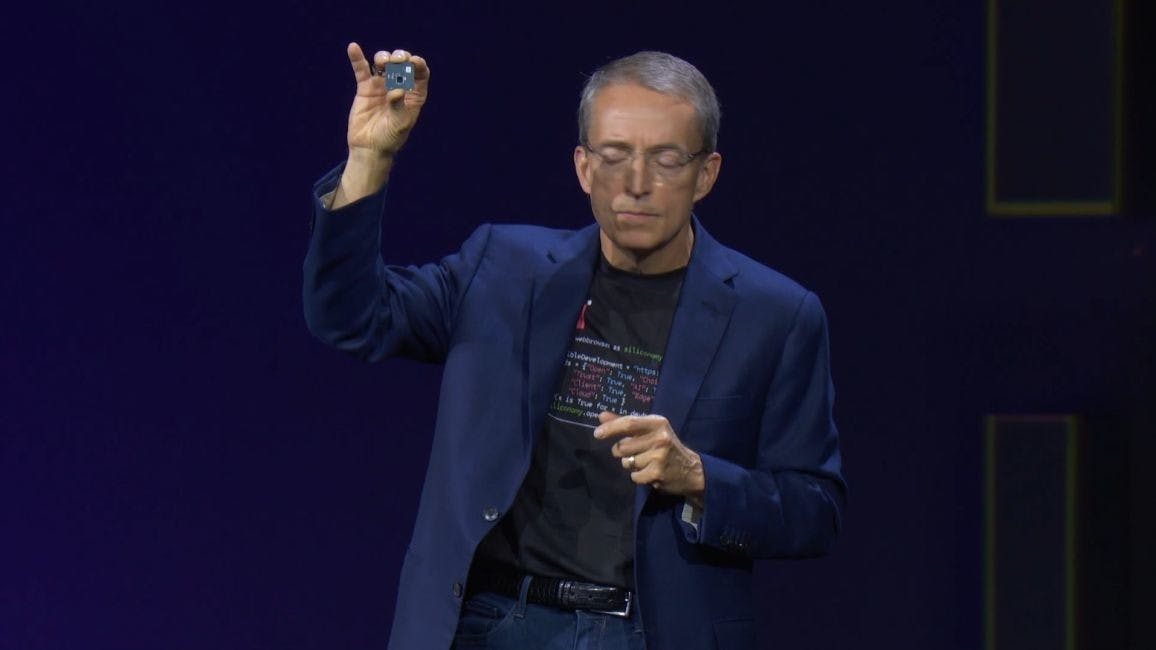

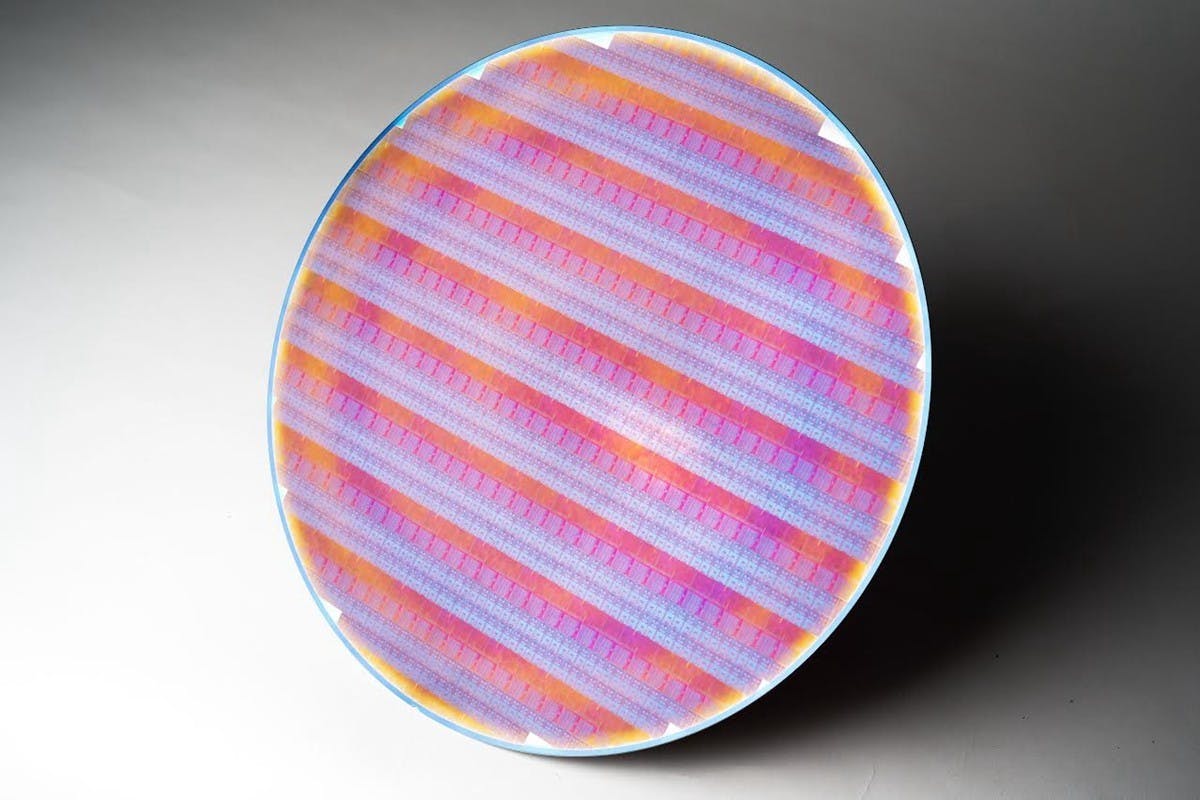

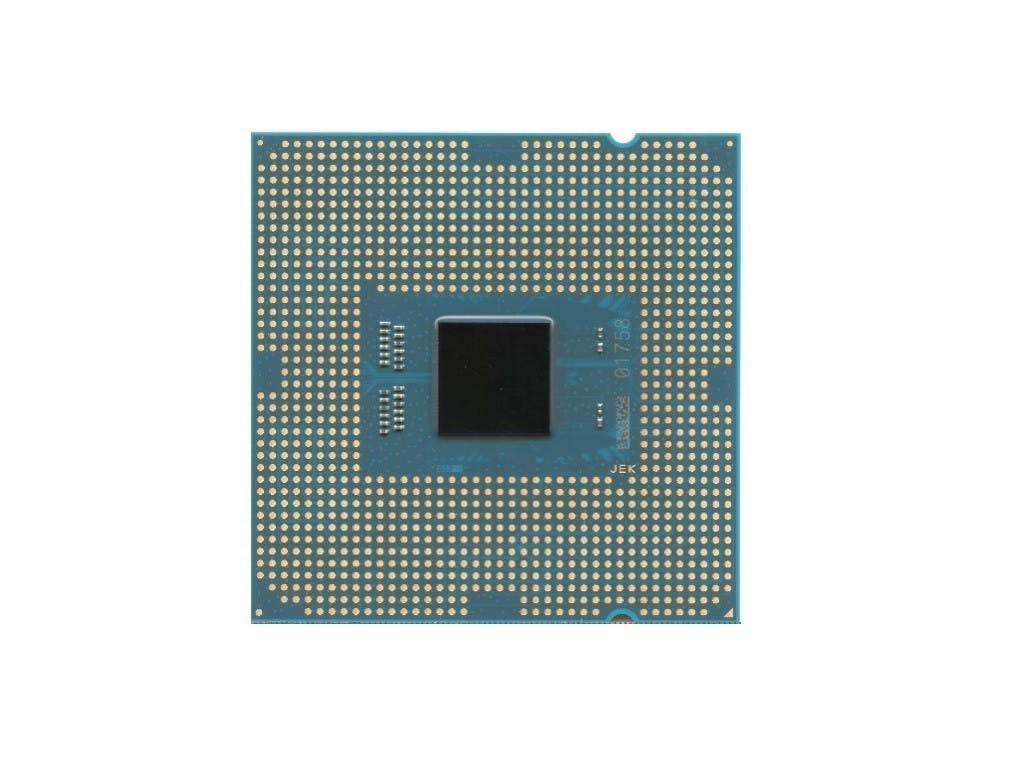

Intel晶圓代工於2024年IEEE國際電子元件會議(IEDM)宣布多項突破性進展,其中透過使用新材料減材釕使電晶體容量得以提升25%,並透過先進封裝的異質整合方式使晶片對晶片的吞吐量提高100%,此外為了進一步推動GAA(環繞式閘極)微縮,Intel晶圓代工同步展示矽RibbonFET CMOS及微縮2D FET閘極氧化物模組成果。 Intel晶圓代工希冀藉展示這些技術進一步實現半導體產業於2030年在單晶片容納1兆電晶體的願景。Intel強調半導體需透過新材料提升如PowerVia晶片背部供電解決方案的效益,並緩解互聯密度與持續微縮的壓力,Intel晶圓代工已設立多項途徑解決銅電晶體與未

7 個月前