Intel歡慶ASML的High NA EUV設備抵達俄勒岡工廠,拍攝運送與架設過程短片

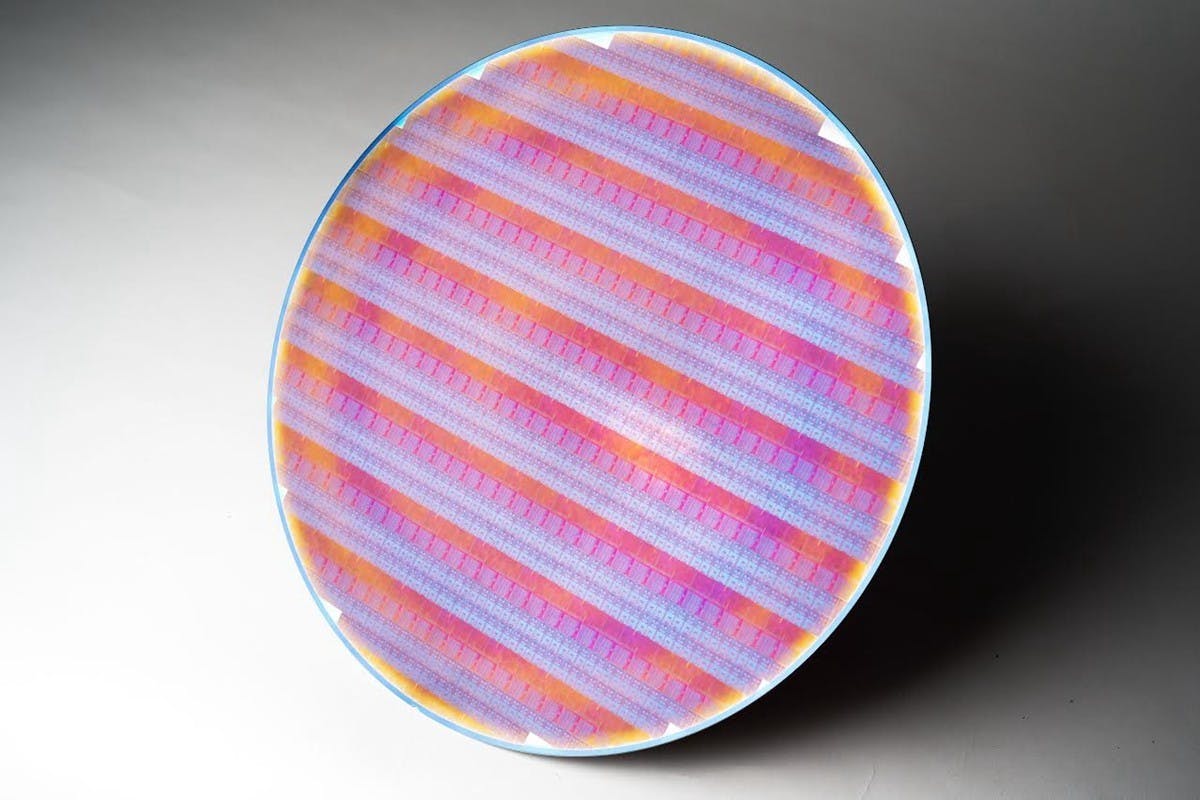

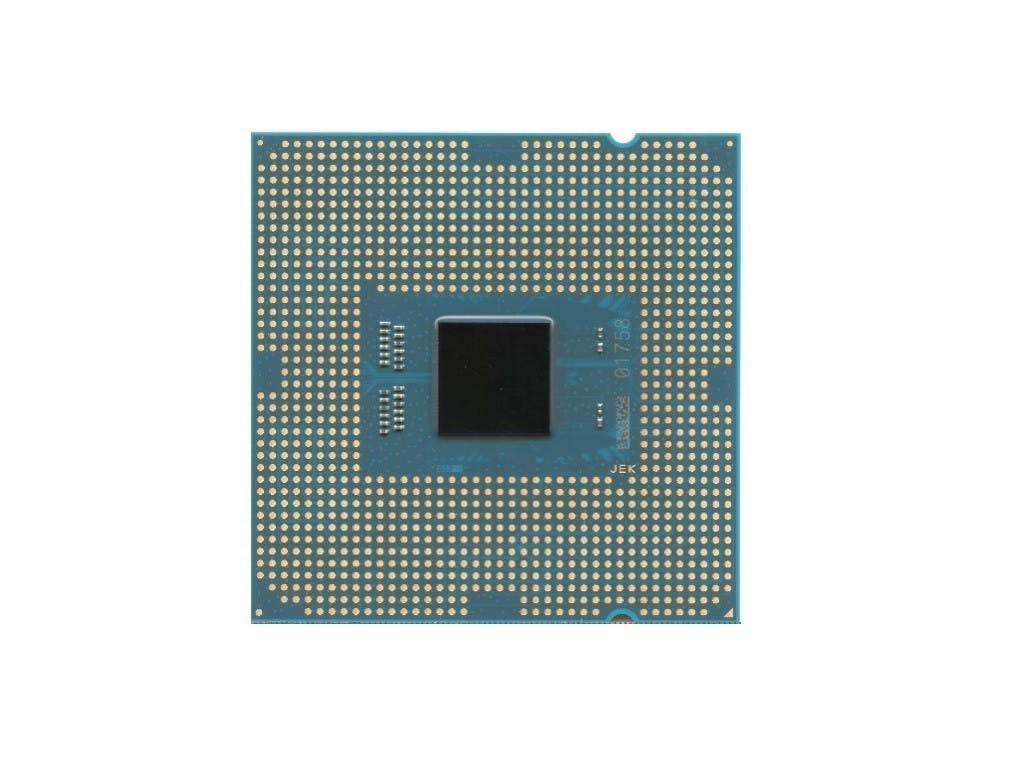

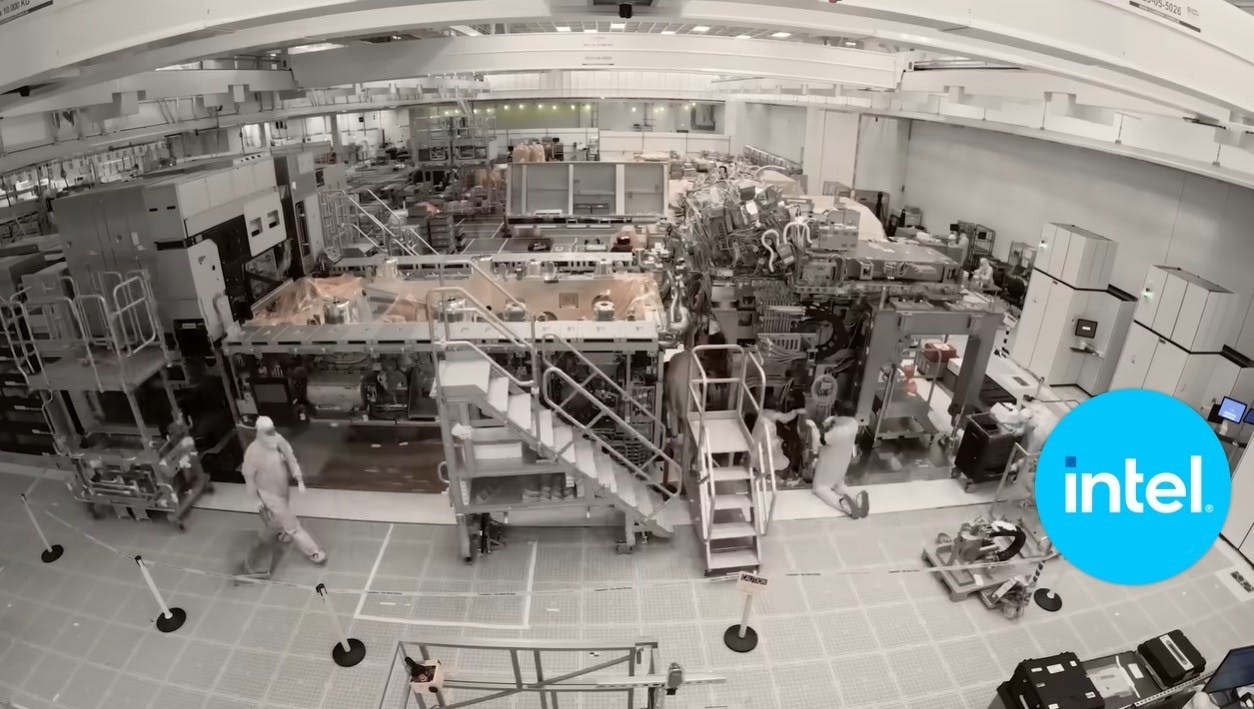

Intel在3月2日釋出一段短片,慶祝ASML的High NA EUV曝光設備正式運抵美國俄勒岡工廠並進行安裝,這套系統是Intel於2022年向ASML訂購新一代曝光機TWINSCAN EXE:5200的關鍵元件,是作為Intel於2025年大規模量產NA EUV計畫的一環,特地拍攝短片也可視為Intel半導體向外界信心喊話的宣傳。 ▲運算階段還在保護的箱體綁了紅緞帶 ▲此次的系統為Intel於2022年下定的新一代ASML曝光設備 Intel已在2018年向ASML訂購前一代的TWINSCAN EXE:5000,而TWINSCAN EXE:5200的NA(數值孔徑)為0.55,相較前一代系

1 年前