聯發科為次代AI與高速運算推出前瞻共封裝光學ASIC設計平台,以高速電子與光學訊號打造小晶片異質整合客製化晶片

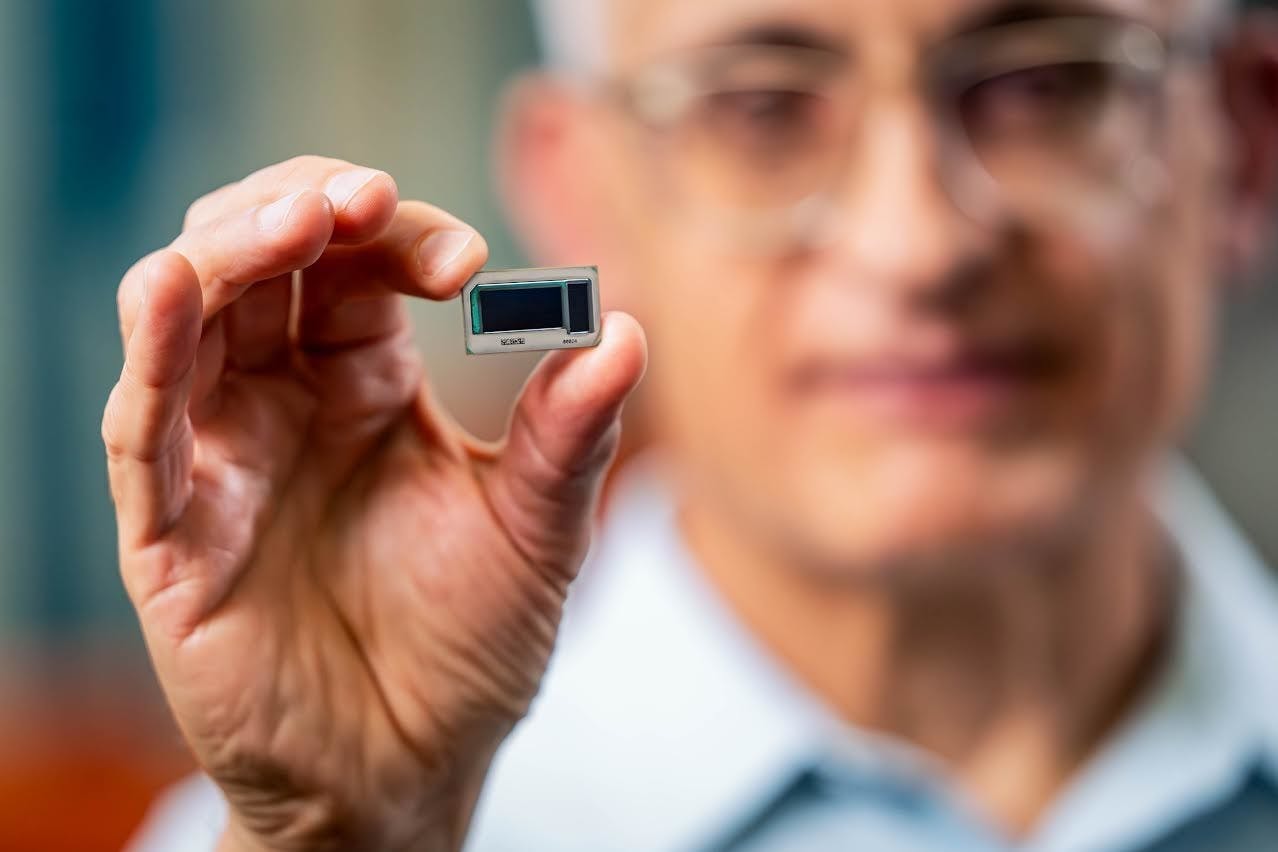

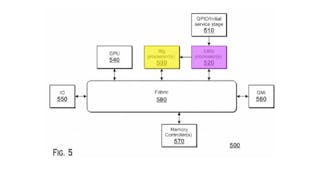

聯發科於2024年光纖通訊大會(OFC 2024)前夕公布前瞻共封裝光學客製化晶片設計平台,提供基於高速電子與光學訊號傳輸介面的異質整合解決方案,結合自研高速SerDes處理電子訊號傳輸,搭配處理光學訊號傳輸的Ranovus Odin光學引擎,利用可拆卸插槽配置8組800Gbps電子訊號鏈路與8組800Gbps光學訊號鏈路,提供便利、高度彈性的客製化晶片配置。 聯發科展示的Co-Package Optics(CPU,異質整合共封裝光學元件)採用112Gbps長距離SerDes與光學模組,相較當前類似的解決方案可進一步縮減電路板面積,降低裝置成本、增加頻寬密度與減少50%傳輸能耗,結合Ranov

1 年前